DRAM은 반도체 중 가격 경쟁이 가장 치열한 시장입니다. 1GB당 단가가 매년 내려가는 산업에서, 일반 DRAM의 5배 가격에 팔리는 제품이 있습니다.

SK하이닉스가 이 제품 하나로 영업이익의 절반 이상을 끌어올렸습니다. 삼성전자는 같은 걸 만들어 엔비디아에 납품하려 했지만, 퀄 테스트에서 번번이 고배를 마셨습니다. 같은 DRAM 칩을 쌓는 건데 결과가 이렇게 다릅니다.

이 격차를 만드는 핵심은 공정 2가지입니다. 그 공정이 뭔지, 왜 수년째 따라잡기 어려운지 3분이면 파악됩니다.

목차

- 같은 DRAM인데 5배 프리미엄, 핵심 공정 2가지

- DRAM 적층 원리, 칩을 쌓는 것만으로는 안 되는 이유

- TSV, HBM 성능을 결정하는 수직 배선

- SK하이닉스 독주의 기술적 근거

- HBM 세대별 로드맵과 투자 모멘텀

- 투자 시 주의사항

1. 같은 DRAM인데 5배 프리미엄, 핵심 공정 2가지

HBM이 일반 DRAM과 가격이 다른 이유는 칩 자체가 아니라 쌓는 기술에 있습니다.

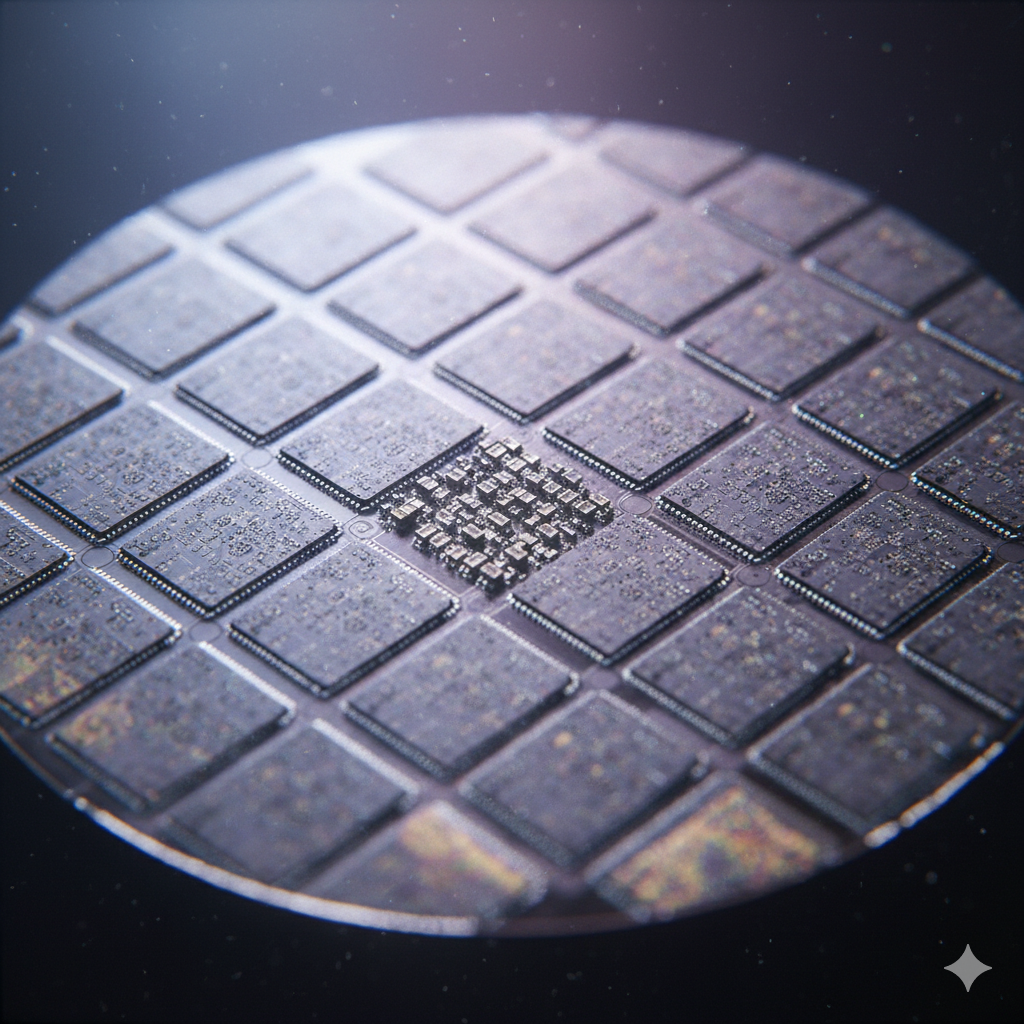

일반 DRAM은 칩 1개를 기판 위에 올려 패키징합니다. HBM은 DRAM 칩을 8~12층으로 수직 적층하고, 칩마다 수천 개의 구멍을 뚫어 전기 신호를 연결합니다. 이 두 가지 공정이 핵심입니다.

- DRAM 다이 적층: 얇게 깎은 DRAM 칩을 정밀하게 쌓아 올리는 공정

- TSV(Through-Silicon Via): 실리콘 웨이퍼에 미세한 구멍을 뚫고 구리를 채워 수직 배선을 만드는 공정

이 두 공정의 수율(양품률)이 곧 원가 경쟁력입니다. 12층을 쌓을 때 한 층이라도 불량이면 전체가 폐기됩니다. 같은 설계도를 갖고 있어도 수율에서 차이가 나면 수익성이 완전히 달라집니다.

2. DRAM 적층 원리, 칩을 쌓는 것만으로는 안 되는 이유

HBM 적층의 출발점은 DRAM 웨이퍼를 50μm 이하로 얇게 가공하는 것입니다. 일반 DRAM 웨이퍼 두께가 약 750μm이니, 1/15 이하로 깎는 셈입니다.

얇게 깎은 다이를 아래부터 한 층씩 쌓아 올립니다. 층과 층 사이는 마이크로 범프라는 미세 솔더볼로 연결합니다. 지름이 수십 μm에 불과한 범프 수천 개가 정확한 위치에 맞물려야 합니다.

적층 공정의 난이도를 높이는 3가지 요인이 있습니다.

- 정렬 정밀도: 층이 늘어날수록 누적 오차가 커짐. 12층 적층 시 허용 오차는 ±1μm 이내

- 열 관리: 다이를 쌓을수록 열이 갇힘. 상층부 온도가 올라가면 성능과 수명이 동시에 하락

- 수율: 12층 기준, 개별 다이 수율이 99%여도 전체 스택 수율은 약 88%로 떨어짐

💡 SK하이닉스는 MR-MUF(Mass Reflow Molded Underfill) 공정을 업계 최초로 양산 적용했습니다. 기존 방식 대비 열 저항을 크게 낮추면서 층간 접착 안정성을 높인 기술입니다. 삼성전자가 엔비디아 퀄 테스트에서 탈락한 주된 원인도 이 열 관리 공정의 차이로 알려져 있습니다.

3. TSV, HBM 성능을 결정하는 수직 배선

TSV는 실리콘 웨이퍼를 관통하는 수직 구리 배선입니다. HBM의 대역폭이 일반 DRAM의 수십 배에 달하는 이유가 바로 이 TSV에 있습니다.

일반 DRAM은 칩 가장자리의 핀을 통해 데이터를 주고받습니다. 병목이 생길 수밖에 없는 구조입니다. 반면 HBM은 다이 전체에 TSV를 배치해 수천 개의 데이터 통로가 동시에 작동합니다. HBM3E 기준 대역폭이 1.18TB/s에 달합니다.

TSV 공정의 핵심 단계는 다음과 같습니다.

- 비아 식각: 실리콘에 지름 5~10μm, 깊이 50μm 이상의 구멍을 수천 개 뚫음

- 절연막 형성: 구리와 실리콘 사이 전기적 간섭을 막는 절연층 코팅

- 구리 충진: 뚫린 구멍에 구리를 빈틈 없이 채움. 보이드(공극)가 생기면 신호 불량

- CMP 평탄화: 표면을 나노미터 수준으로 평탄하게 연마

⚠️ TSV 1개라도 불량이면 해당 스택 전체의 대역폭에 영향을 줍니다. 12층 스택에서 TSV 불량률을 0.001% 이하로 관리해야 상용 수준의 수율이 나옵니다. 이 미세 공정 관리 역량이 SK하이닉스와 경쟁사의 격차를 만드는 핵심입니다.

4. SK하이닉스 독주의 기술적 근거

SK하이닉스가 HBM 시장 점유율 50% 이상을 유지하는 이유는 설계가 아니라 양산 공정 역량에 있습니다.

📌 MR-MUF 공정 독점

- 업계 유일의 양산 적용 업체. 열 방출 성능에서 경쟁사 대비 우위

- 엔비디아 H100·H200·B200 GPU에 탑재되는 HBM3E를 독점 공급

📌 TSV 수율 격차

- 12층 적층 기준 양품률에서 삼성전자 대비 유의미한 차이

- 이 수율 차이가 원가와 납기 양쪽에서 경쟁력으로 작용

📌 선행 세대 양산 이력

- HBM2E, HBM3, HBM3E 모두 업계 최초 양산

- 각 세대에서 축적한 공정 데이터가 다음 세대 수율 안정화를 앞당김

💡 HBM4부터는 게임 체인저가 될 수 있습니다. 마이크로 범프 대신 하이브리드 본딩 방식으로 전환됩니다. 층간 연결 면적이 줄어들어 더 많은 층을 쌓을 수 있지만, 완전히 새로운 공정이기 때문에 기존 수율 격차가 리셋될 가능성도 있습니다.

5. HBM 세대별 로드맵과 투자 모멘텀

HBM 세대 교체 시점이 곧 투자 모멘텀입니다.

- HBM3E (현재 주력): 8~12층 적층, 대역폭 1.18TB/s. 엔비디아 B200·B300 시리즈 탑재

- HBM4 (2026년 하반기 양산 목표): 16층 이상, 하이브리드 본딩 전환. 엔비디아 차세대 GPU용

- HBM4E (2027년 이후): 대역폭 2TB/s 이상 목표

단기 촉매

- 엔비디아 B300 시리즈 출하 확대에 따른 HBM3E 수요 증가

- SK하이닉스 HBM 분기별 매출 성장률 추이

중기 촉매

- HBM4 양산 시점 확정 및 엔비디아 퀄 테스트 통과 여부

- 삼성전자 HBM3E 엔비디아 퀄 통과 시 경쟁 구도 변화

장기 촉매

- 하이브리드 본딩 전환 이후 수율 안정화 속도

- AI 서버 시장 성장률에 연동된 HBM 수요 전망

6. 투자 시 주의사항

HBM 기술 우위가 곧 주가 상승을 보장하지는 않습니다.

- DRAM 사이클 리스크: HBM 비중이 높아져도 SK하이닉스 전체 매출의 상당 부분은 여전히 범용 DRAM. 업황 하락기에는 HBM 호조만으로 주가 방어가 어려울 수 있음

- 경쟁사 추격: 삼성전자가 HBM3E 퀄 테스트를 통과할 경우 가격 경쟁 압력 발생. 마이크론도 HBM 생산 확대 중

- 기술 전환 리스크: HBM4의 하이브리드 본딩은 기존 MR-MUF 우위를 무력화할 수 있음. 새 공정에서 수율 선점 여부가 변수

- 밸류에이션 부담: AI 수혜주 프리미엄이 이미 주가에 반영되어 있을 가능성. 실적 대비 주가 수준을 반드시 확인

마무리

SK하이닉스 HBM의 핵심은 설계가 아니라 적층 공정과 TSV 수율에 있습니다.

- HBM 프리미엄의 원천은 DRAM 다이 적층과 TSV 수직 배선, 두 가지 공정의 양산 수율

- SK하이닉스의 MR-MUF 공정과 선행 양산 이력이 현재 독주의 근거

- HBM4 하이브리드 본딩 전환 시점이 경쟁 구도를 바꿀 변수

HBM4 양산 일정과 삼성전자 퀄 테스트 결과를 반드시 추적하세요. 기술 전환기에 수율 선점 여부가 향후 2~3년의 실적 격차를 결정합니다.

본 글은 투자 참고용 정보이며, 투자 판단과 책임은 본인에게 있습니다.

알아두면 좋은 정보:

SK하이닉스 매출 구조 분석, 97조의 비밀은 HBM이 아니다 (2026년)

SK하이닉스 HBM4 vs HBM3E 차이점 비교, 대역폭 2.7배 차이의 비밀

SK하이닉스 패키징 기술 MR-MUF, 삼성 NCF와 다른 HBM 1위인 이유

SK하이닉스 NAND, 2026년 적자 사업부가 13조 벌어온다

SK하이닉스 1c DRAM 공정, 9배 증산 계획의 핵심 정리

댓글